### The Future of SSD Architectures

### Eyal Bek – SSD Product Marketing Avi Klein – Memory Technology SanDisk

# IS 5% ENOUGH?

| HDD  | SSD                                                                                                                |

|------|--------------------------------------------------------------------------------------------------------------------|

| 1 TB | 128GB                                                                                                              |

|      | <ul> <li>Instant On</li> <li>Lightweight</li> <li>Slim</li> <li>Longer<br/>battery life</li> <li>Rugged</li> </ul> |

Source: analysts average PC SSD attach rate: 2010

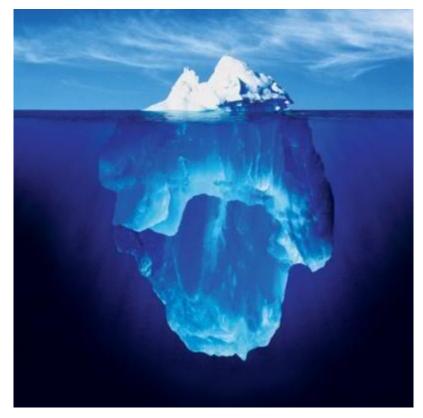

# Cutting SSD Cost Is Needed to Drive Growth

SSD ASP vs. PC ASP

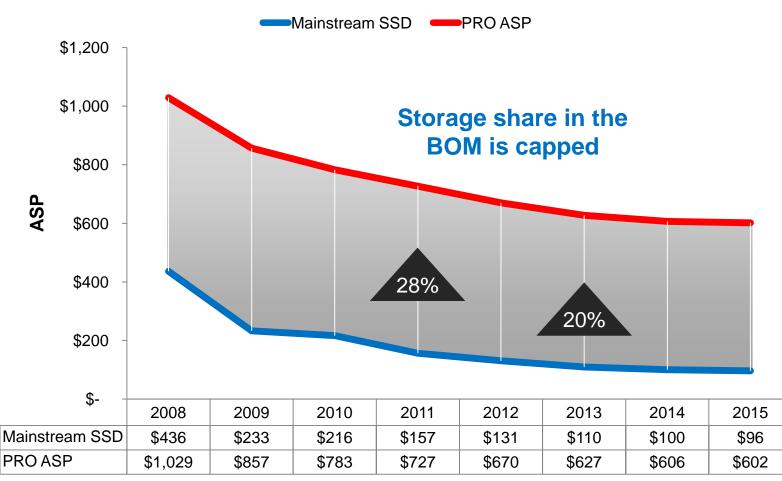

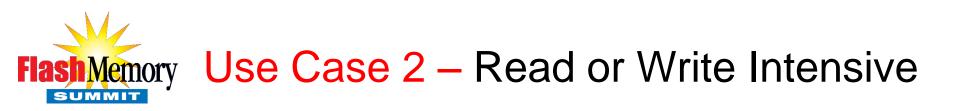

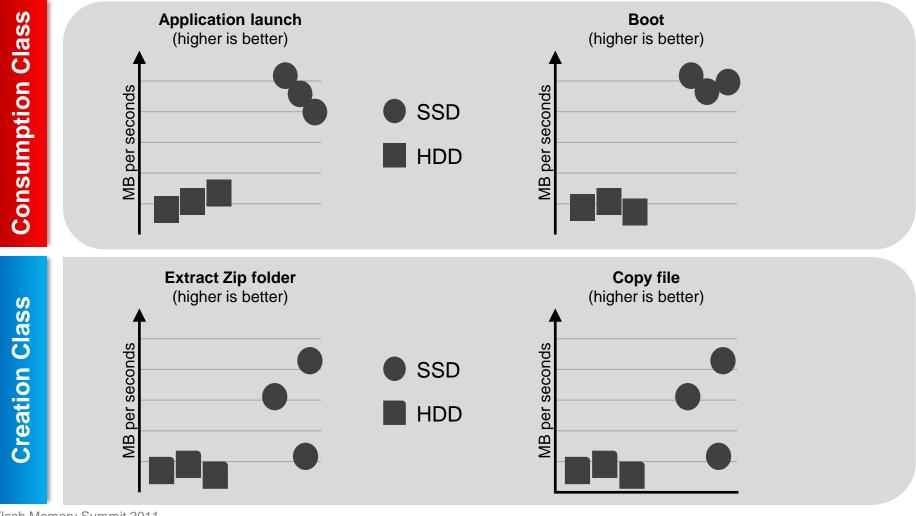

### Use Case 1 – Super Fast Side Loading

**AJA System Test**

(\*) copy time in seconds for HD movie **Source:** http://www.pcmag.com/article2/0,2817,2388114,00.asp

Flash Memory Summit 2011 Santa Clara, CA

Source: Sandisk internal testing

SanDis

- 1. Outlook

- 2. Windows Media Player,

- 3. Internet Browser (Download)

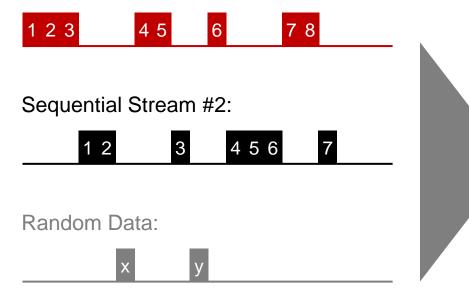

#### Sequential Stream #1:

#### 1 2 3 1 2 x 4 5 3 y 6 4 5 6 7 8 7

**Driver Mixes All Writes**

### Use case 4 –

Instant On without Losing Battery Life

### What's Wrong with Existing Sleep?

- Empties battery as memory remains powered

- Not safe loss of last saved work in case of power outage

### New Deep Sleep Enabled by SSD's

- Data in memory is saved in hiberfil.sys

- Computer can shutdown completely achieving much longer standby time

- Safe data is saved

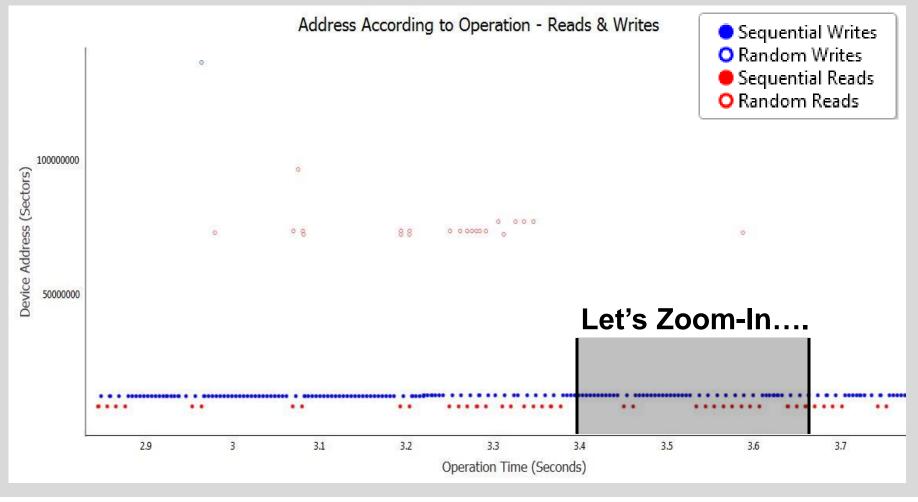

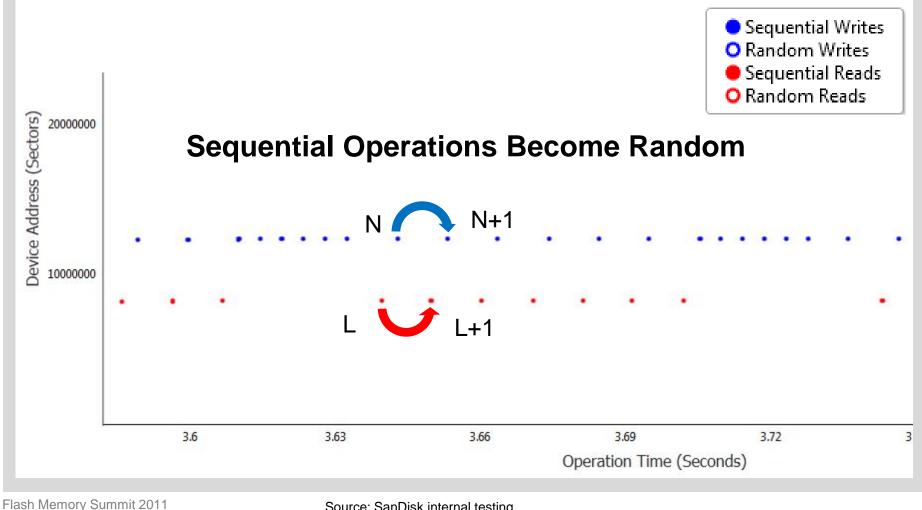

# In-depth Analysis of Real Computing Usage Workload: Copy File Example

Flash Memory Summit 2011 Santa Clara, CA

Source: SanDisk internal testing

SanDisk<sup>®</sup>

#### Santa Clara, CA

Source: SanDisk internal testing

SanDis

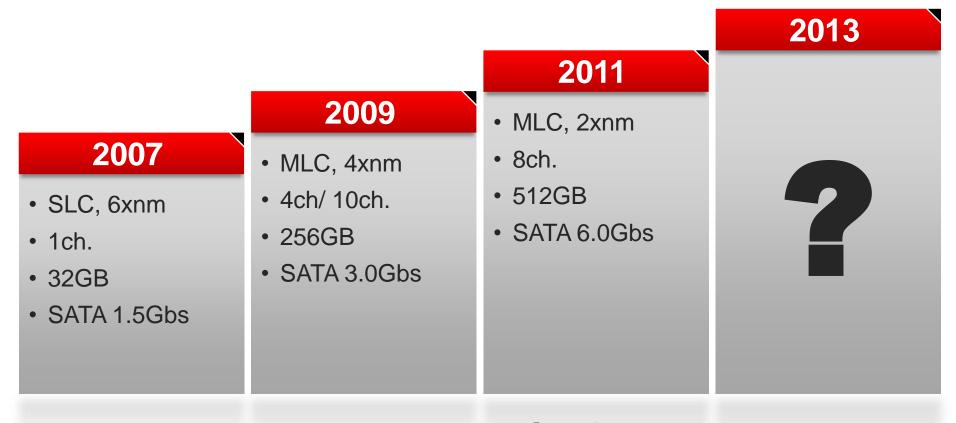

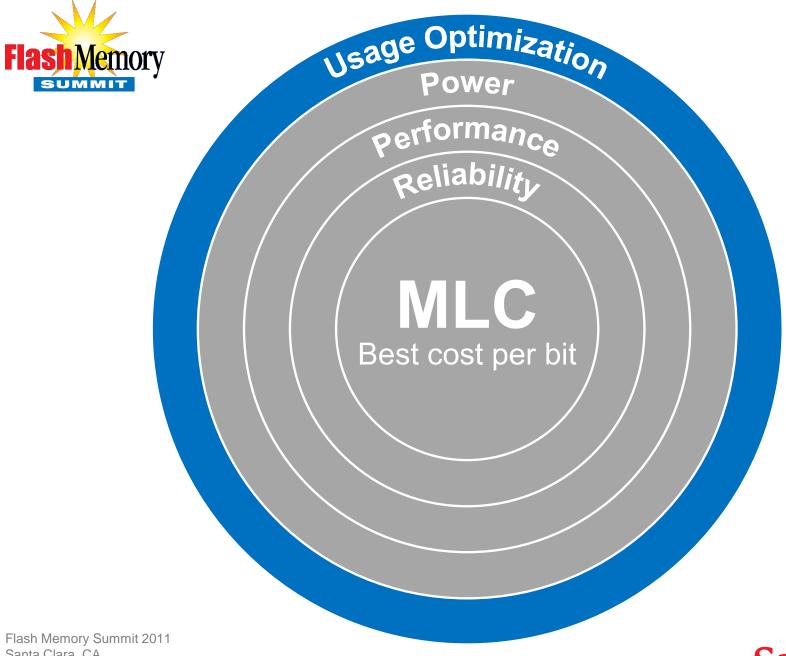

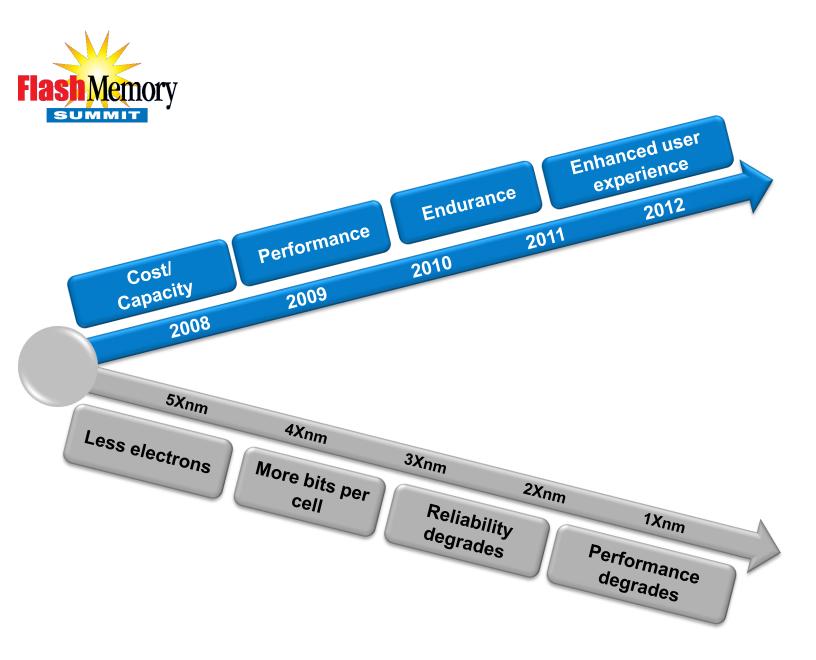

# Memory SSD Architecture Evolution

### How Do We Keep Scaling and Provide Performance and Reliability of SSD?

Flash Memory Summit 2011 Santa Clara, CA

### SanDisk<sup>• 10</sup>

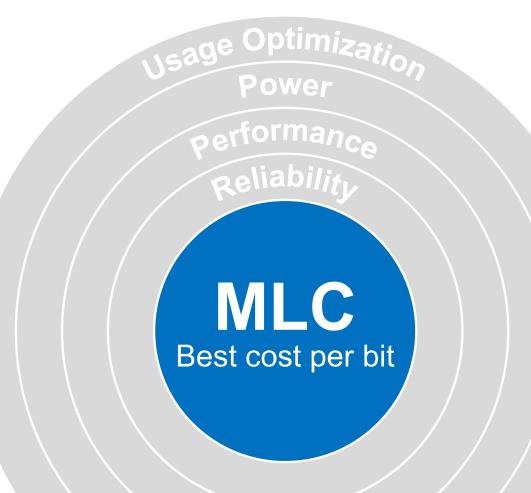

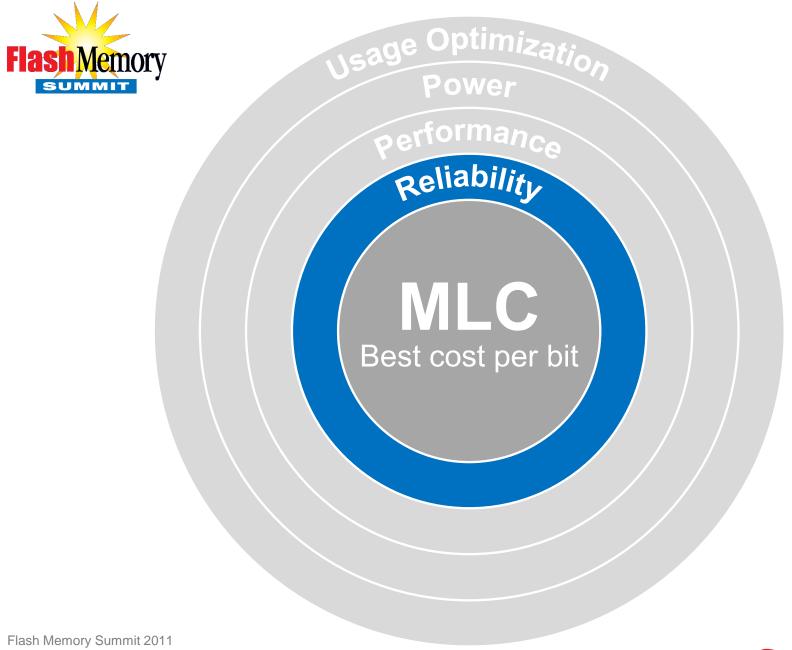

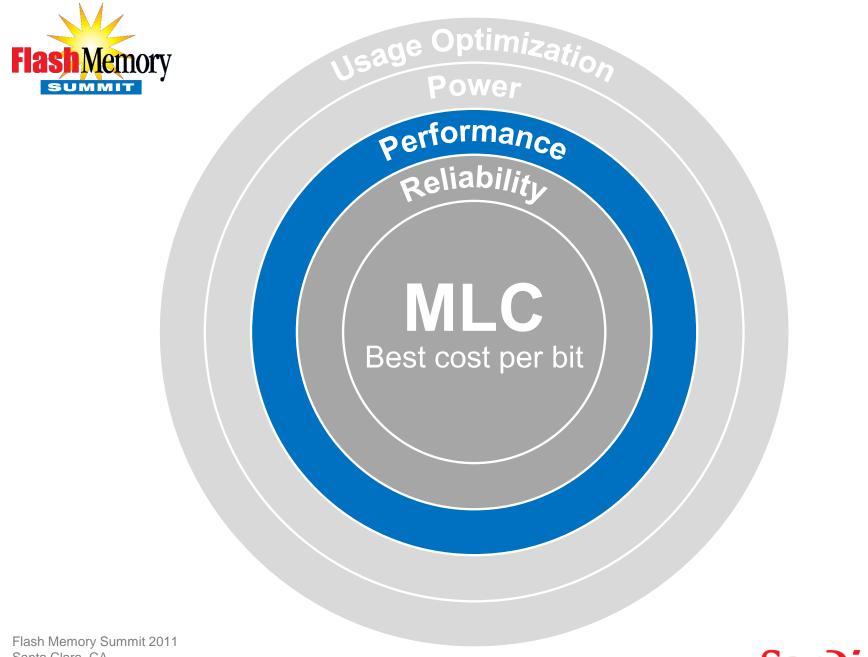

# Flash Memory Features Tailored for Usage Scenario

| USE Case             | Challenge | Architecture Features (examples) |

|----------------------|-----------|----------------------------------|

| Multi<br>Tasking     |           |                                  |

| Fast Side<br>Loading |           |                                  |

| Instant On           |           |                                  |

# Flash Memory Features Tailored for Usage Scenario

| USE Case             | Challenge                                           | Architecture Features (examples)                                                          |

|----------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------|

| Multi<br>Tasking     | OS driver mixes<br>commands, data<br>becomes random | Flow prediction, hot/cold sorting,<br>Effective management of pseudo<br>random operations |

| Fast Side<br>Loading |                                                     |                                                                                           |

| Instant On           |                                                     |                                                                                           |

# Flash Memory Features Tailored for Usage Scenario

| USE Case             | Challenge                                           | Architecture Features (examples)                                                          |

|----------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------|

| Multi<br>Tasking     | OS driver mixes<br>commands, data<br>becomes random | Flow prediction, hot/cold sorting,<br>Effective management of pseudo<br>random operations |

| Fast Side<br>Loading | Fast sequential write,<br>higher peak power         | Parallel Multi die / Plane interleave<br>Thermal throttling                               |

| Instant On           |                                                     |                                                                                           |

# Features Tailored for Usage Scenario

| USE Case             | Challenge                                           | Architecture Features (examples)                                                          |

|----------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------|

| Multi<br>Tasking     | OS driver mixes<br>commands, data<br>becomes random | Flow prediction, hot/cold sorting,<br>Effective management of pseudo<br>random operations |

| Fast Side<br>Loading | Fast sequential write,<br>higher peak power         | Parallel Multi die / Plane interleave<br>Thermal throttling                               |

| Instant On           | Multiple power off/on<br>Access to first I/O        | Quick mount<br>Optimize single thread read                                                |

What Changed?

#### **3 Leveled Cost Reduction:**

#### NAND Process

- 24nm in Mass Production

- Migrating to 19nm in H2/2011

- Expected to Continue Scaling

#### 3-bits-per-cell

Mature 4th Generation 3-bits-per-cell Technology

#### High Capacity Die

- 24nm 2-bit-per-cell 64Gb

- 19nm 3-bit-per-cell 128Gb

- Less Die Stacking for a Given Capacity

Santa Clara, CA

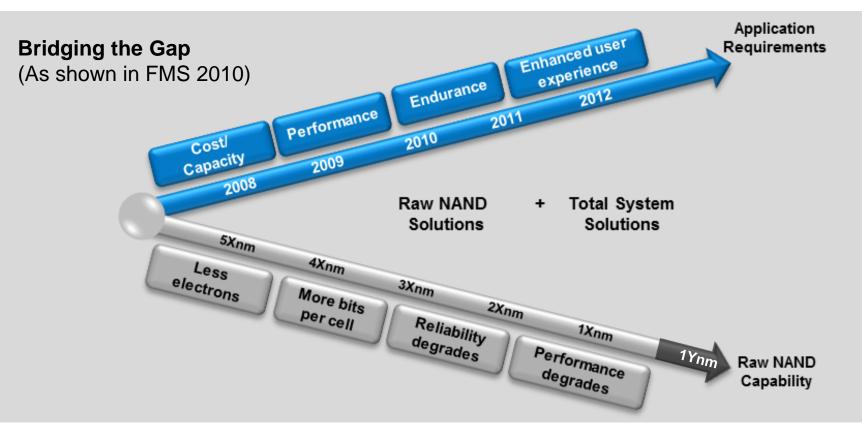

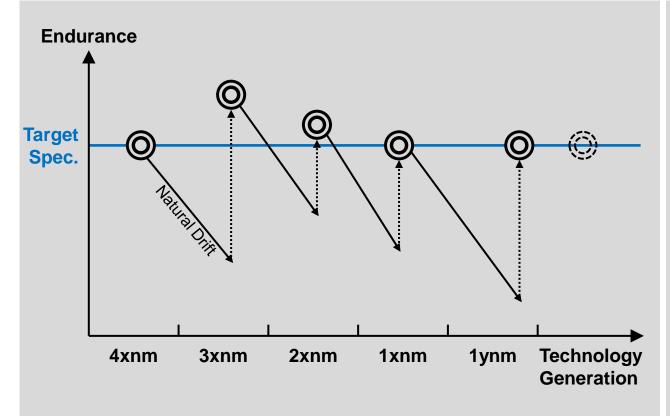

# Enhancing NAND Technology Reliability

Based on SanDisk Internal Evaluation

#### Goal:

Maintain Endurance Target while Scaling – Overcome Natural Drift

- 1) Increase VT Window

- 2) Dynamic Read

- 3) Air Gap

- 4) Proprietary Process, Cell & Programming Scheme Optimization

- 5) Data Randomization / Scrambling

- 6) nCache™

- 7) Hybrid FG Cell Design

- 8) <u>StrongECC™ + DSP</u>

SanDisk<sup>• 20</sup>

Santa Clara, CA

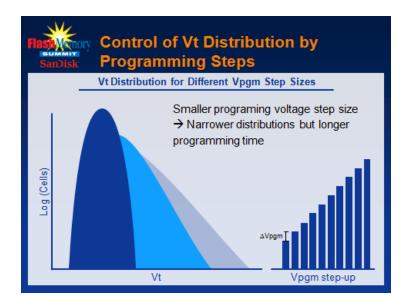

# Enhancing NAND Technology – Sequential Performance

#### **Goal:** Maintain **Performance** while Scaling – Overcome Natural Drift

- Larger Page Size

- All Bit Line Architecture (ABL)

- Parallelism:

- Multi-Plane in a Die

- Multi Die in a Product

- Bus performance (e.g. Toggle Mode)

- StrongECC™+ DSP

Source: Klein/Oren FMS 2010

#### **Enable Higher Performance Level**

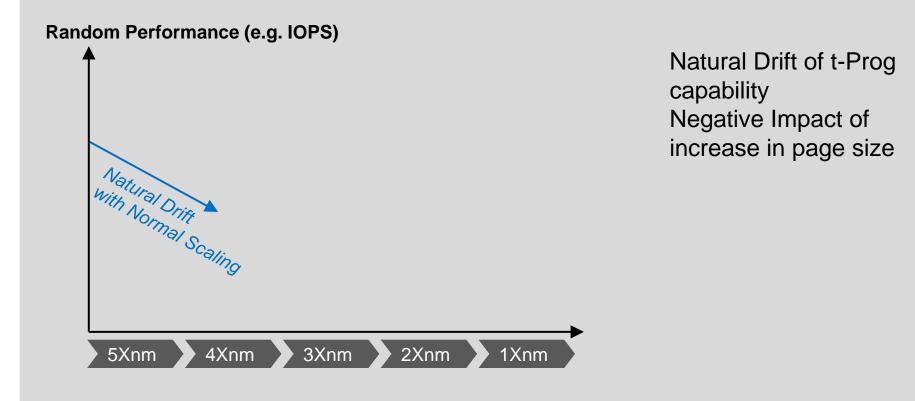

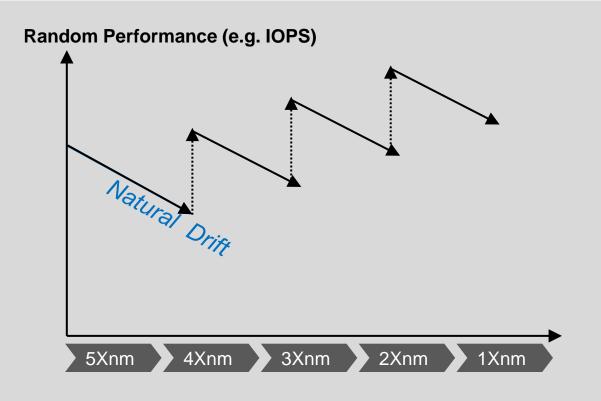

# Enhancing NAND Technology – Random Performance

Based on SanDisk Internal Evaluation

#### Goal: Maintain Random Performance while Scaling – Overcome Natural Drift

# Enhancing NAND Technology – Random Performance

Based on SanDisk Internal Evaluation

#### Goal: Maintain *Random Performance* while Scaling – Overcome Natural Drift

- 1) Cache Technology and Optimization per usage

- 2) Page Based Mapping

- 3) Proprietary WL/BL RC reduction

- 4) StrongECC<sup>™</sup> + DSP

Optimized for

Random

Performance

#### Flash Memory Summit 2011 Santa Clara, CA

### SanDisk<sup>• 24</sup>

Santa Clara, CA

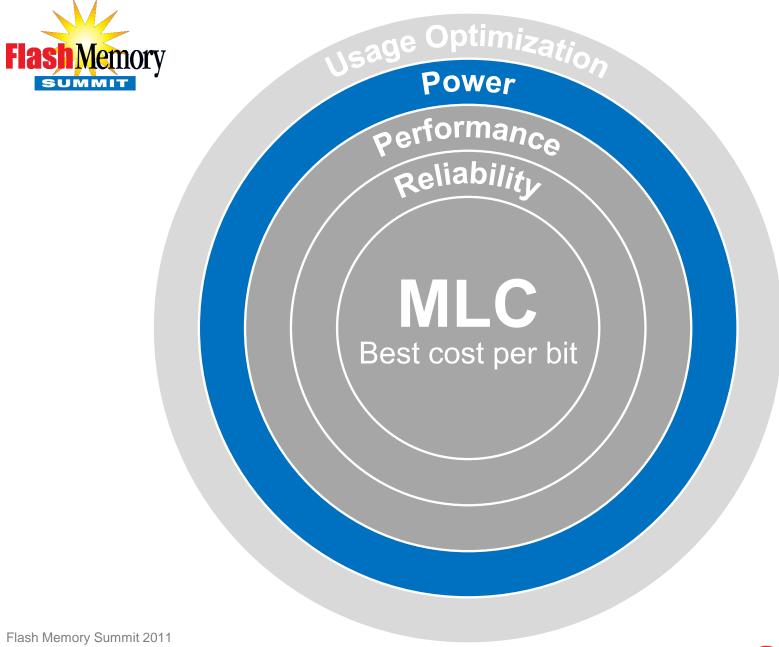

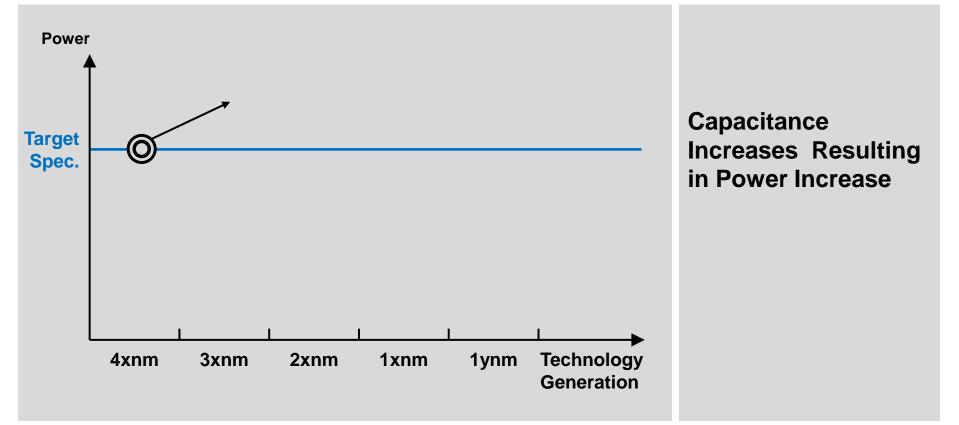

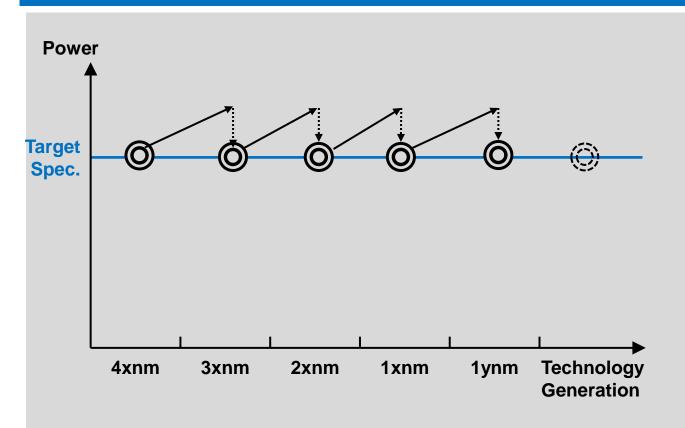

Based on SanDisk Internal Evaluation

#### Goal: Maintain Power / Energy Target while Scaling

# Enhancing NAND Technology – Power

Based on SanDisk Internal Evaluation

#### Goal: Maintain Power / Energy Target while Scaling

- 1) Proprietary ICC Optimization

- 2) ABL (All Bit Line) Design Enables Lower Energy per bit

- 3) Dynamic Power Conscious Parallelism

- 4) Proprietary Low PowerStrongECC<sup>™</sup> + DSP

- 5) Proprietary Low Leakage CMOS

- 6) AirGap Reduces Capacitance

### SanDisk<sup>• 27</sup>

Santa Clara, CA

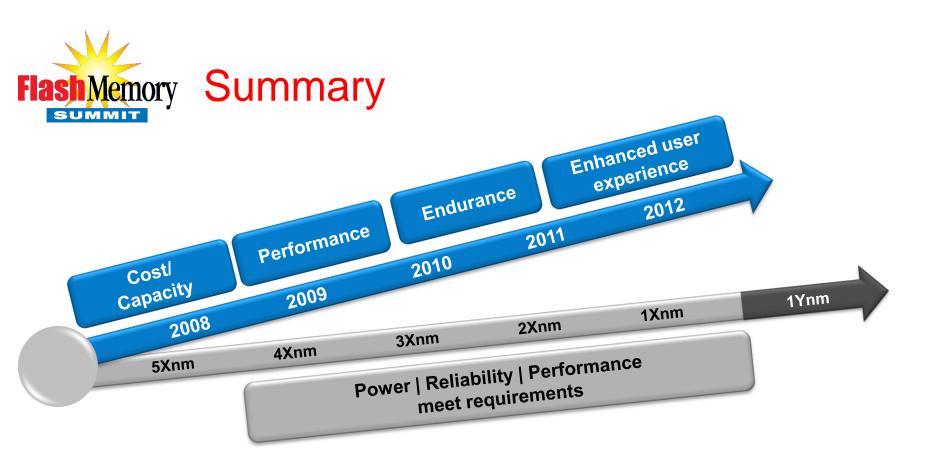

NAND + System solutions enable continuation of NAND scaling while maintaining reliability, performance & power requirements

- SSD enables a multitude of opportunities in mobile computing

- It is up to us to bring the SSD technology to mainstream

- This is achievable by:

- Continuous process shrink

- Tailoring solutions to use cases

System design based on real life usage data for enhanced real life user experience

Flash Memory Summit 2011 Santa Clara, CA

### SanDisk<sup>• 31</sup>

### **Thank You**