### Designing Scalable, Configurable Controllers for SSDs

### Narinder Lall – eASIC Corporation Santa Clara, August 2011

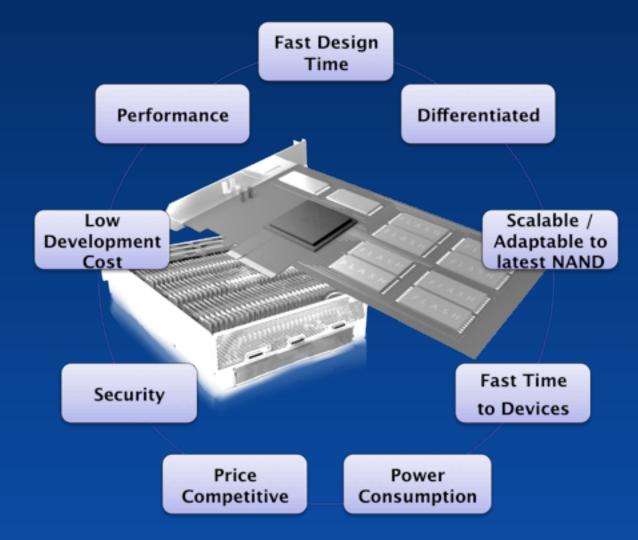

## Traditional SSD Design Options

|                       | FPGA         | ASSP         | Cell-based ASIC |

|-----------------------|--------------|--------------|-----------------|

| Low Development Cost  | $\checkmark$ | $\checkmark$ |                 |

| Fast Design Time      | $\checkmark$ | $\checkmark$ |                 |

| Scalable/Adaptable    | $\checkmark$ |              | $\checkmark$    |

| Differentiated        | $\checkmark$ |              | $\checkmark$    |

| Fast Time to Devices  | $\checkmark$ | $\checkmark$ |                 |

| Power Consumption     |              | $\checkmark$ | $\checkmark$    |

| Price Competitiveness |              | $\checkmark$ | $\checkmark$    |

| Performance           |              | ✓            | $\checkmark$    |

| Security              |              |              | $\checkmark$    |

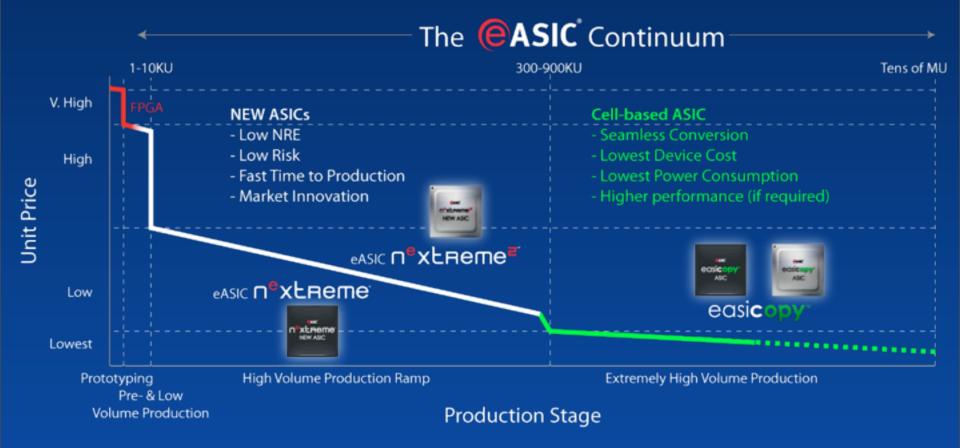

#### NEW ASIC: A New Design Platform

|                       | eASIC<br>NEW ASICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Comments                                      |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Low Development Cos   | t 🧹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A fraction the cost of cell-based ASIC        |

| Fast Design Time      | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Right by construction design – simpler design |

| Scalable/Adaptable    | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Many family members/configurable interfaces   |

| Differentiated        | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Uniquely configurable using one via-layer     |

| Fast Time to Devices  | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Only one layer changes from design to design  |

| Power Consumption     | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50-80% lower power than an FPGA               |

| Price Competitiveness | <ul> <li>Image: A second s</li></ul> | Shipping in volume in PC hybrid-drives        |

| Performance           | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Between FPGA and Cell-based ASIC              |

| Security              | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | No external bit-stream or software access     |

|                    | NEW ASIC |          |                                | Cell-based ASIC       |

|--------------------|----------|----------|--------------------------------|-----------------------|

|                    |          | NEW ASIC | exer<br>n®xtReme#*<br>NEW ASIC | easicopy<br>ASIC      |

| Max. Logic Cells   | 360K     | 740K     | 580K                           |                       |

| Max. bRAM (Mb)     | 5.6      | 11.5     | 16.5                           | Seamless<br>Migration |

| Max bRAM (#blocks) | 175      | 320      | 468                            | From<br>NEW ASIC      |

| Max I/Os           | 790      | 792      | 630                            | To Cell-based<br>ASIC |

| Max 6.5Gbps SERDES |          | -        | 32                             |                       |

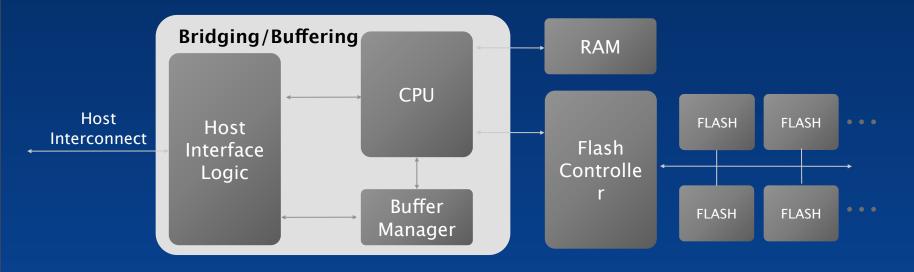

### Generic SSD Functional Diagram

- Performance Throughput

- Flexible Interconnects

• Quickly adaptable to support the latest FLASH

Santa Clara, CA August 2011

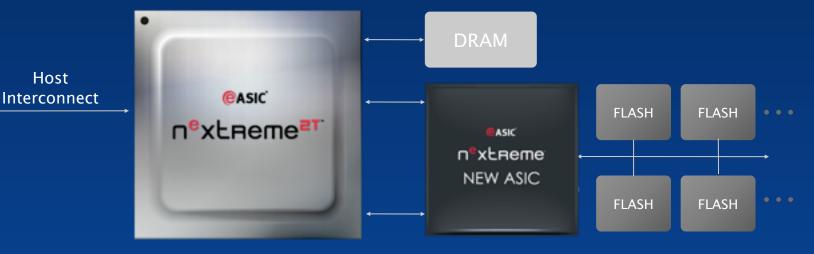

#### eASIC Devices for SSDs

#### Customized Bridging/Bufferng

- 32-bit CPUs

- PCle

- SAS

- SATA

- Proprietary Interfaces

#### Customized Flash Controller

- ONFI / Toggle

- Proprietary Interfaces

Santa Clara, CA August 2011

# Right by Construction Design

|                             | From FPGA to eASIC NEW ASIC    |  |  |

|-----------------------------|--------------------------------|--|--|

| Design Conversion           | eASIC (or customer)            |  |  |

| Timing Constraints          | eASIC (or customer)            |  |  |

| Testbench                   | Customer                       |  |  |

| RTL Simulation              | Customer                       |  |  |

| Synthesis                   | eASIC (or customer)            |  |  |

| DFT Insertion               | Not Required                   |  |  |

| Power Mesh Design           | Not Required                   |  |  |

| I/O Ring Design             | Not Required                   |  |  |

| Clock Tree Synthesis        | Not Required                   |  |  |

| Package/Substrate<br>Design | Not Required                   |  |  |

| IR Drop                     | Not Required                   |  |  |

| Placement                   | eASIC (or customer)            |  |  |

| Routing                     | eASIC                          |  |  |

| Extraction                  | eASIC                          |  |  |

| LVS/DRC                     | eASIC                          |  |  |

| STA                         | eASIC                          |  |  |

| ATPG                        | eASIC (only one layer changes) |  |  |

| Formal Verification         | eASIC                          |  |  |

FF

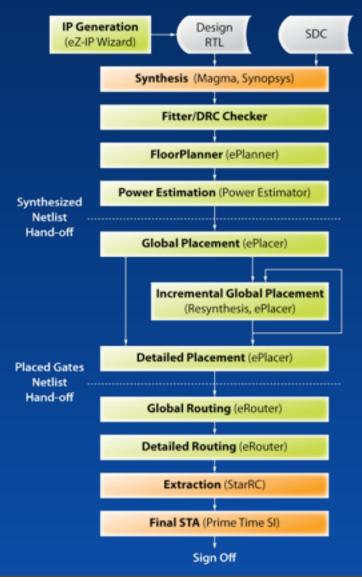

Flash Design Flow

- 1. Convert FPGA PLLs, bRAMs, I/Os to eASIC using IP generators within eASIC eTools

- Synthesize using Magma or Synopsys

- Floor planning / create optimal region placements

- Optional power estimation

- Global and detailed placement using eASIC's ePlacer

- 2. Routing of vias using eASIC's eRouter

- Extraction and STA using ASIC grade tools

- Formal verification after every stage using ASIC grade tool

Thursday, August 11, 2011

- eASIC NEW ASICs enable design of scalable, configurable SSD controllers

- Lower cost and power than FPGAs

- Simple to design like FPGAs Right by construction design

- Single via-layer configurable for fast design & manufacturing time

- Enhanced security No FPGA-like external bit-stream

- Multiple devices for scalable solutions

- Already shipping in SSDs